In diesem Grundlagenteil geht es um eine weitere wichtige Schaltung: dem Multiplexer / Demultiplexer.

Multiplexer (Mux) schalten von vielen Eingängen auf einen Ausgang.

Demultiplexer (Demux) schalten von einem Eingang auf viele Ausgänge.

Anschaulich erklären lässt sich die Funktionsweise mit einem Bauteil mit z.B. einem Eingang und n-Ausgängen. Der gewünschte Ausgang wird per Drehschalter ausgewählt. Das Eingangssignal wird zum gewählten Ausgang durchgeleitet. Natürlich funktioniert dies auch umgekehrt mit n-Eingangsleitungen und einer Ausgangsleitung – hier wird die gewünschte Eingangsleitung ausgewählt, welche zum Ausgang durchgeleitet werden soll.

In der Elektronik erfolgt die Selektion des gewünschten Ein- oder Ausgangs natürlich nicht per Drehschalter, sondern elektronisch.

Der Vorteil hierbei liegt darin, dass neben der eigentlichen Datenleitung zusätzlich nur wenige Adressleitungen zur Selektion benötigt. Beispiel: Zur Selektion von 8 Eingangs- oder Ausgangsleitungen werden nur 3 Adressleitungen benötigt ( \(2^3=8\) ).

Bei zyklischem Durchlauf können mit einem Multiplexer parallele Datenströme in serielle gewandelt werden. Diese können somit über eine einzige Datenverbindung wie Glasfaser oder eine Telefonleitung übertragen werden und in Verbindung mit einem Demultiplexer wieder in parallele Daten gewandelt werden.

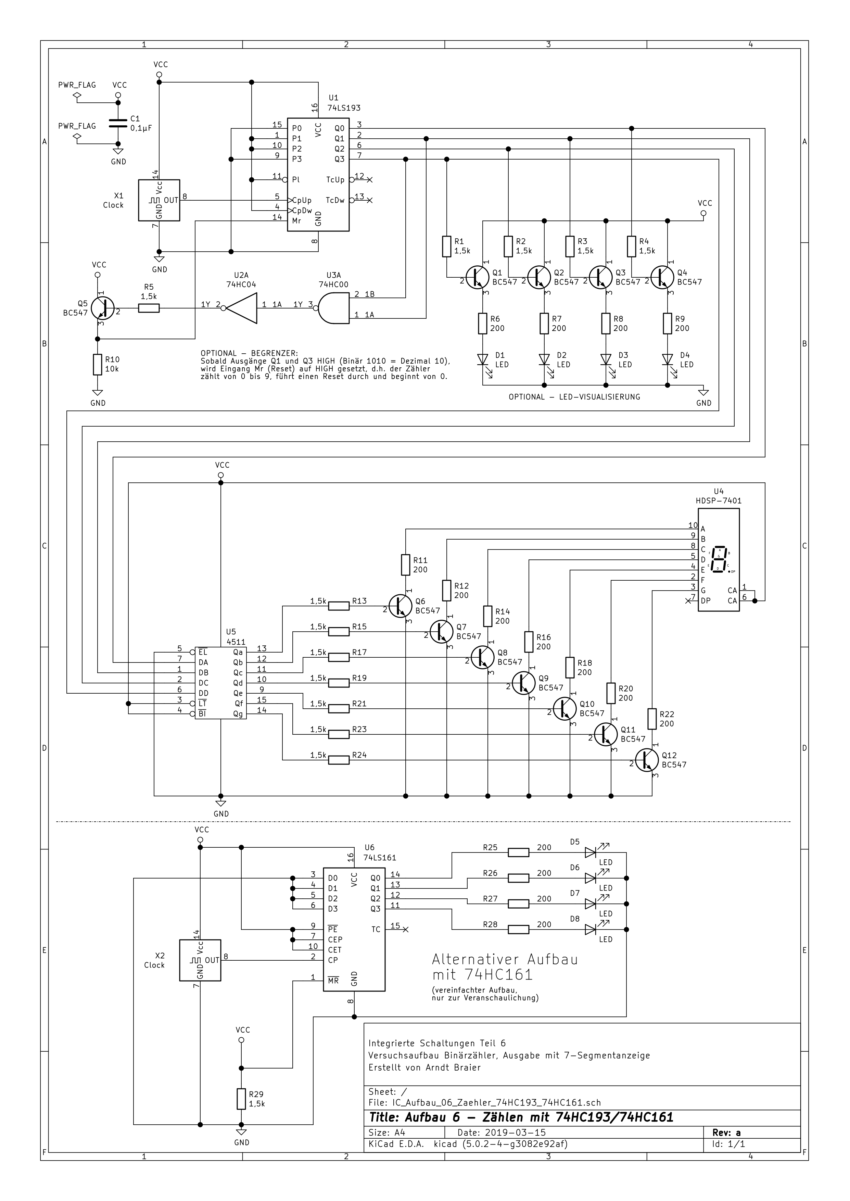

Der untere Aufbau zeigt einen Demultiplexer, hier wird nämlich ein Eingangssignal an Pin 3 (X) zu einem ausgewählten Ausgang X0-X7 durchgeschaltet. Die Selektion (mit dem „elektronischen Drehschalter“) erfolgt über die entsprechende Ansteuerung der Eingänge A bis C.